-Time allowed: 3 hours

-Maximum degree: 90

-Attempt all the 7 questions

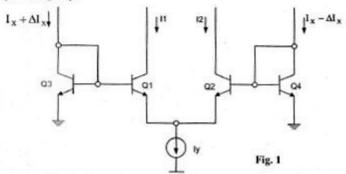

# Problem (1) [10 pts]:

A basic two quadrant multiplier is shown in Fig.1. All transistors are assumed matched.

- (a) Find the relation between  $I_{out} = (I_1 I_2)$  and the inputs  $\Delta I_x$  and  $I_y$ .

- (b) Design the circuit needed to obtain a differential output current from an input voltage V<sub>χ</sub>, and the circuit needed to obtain an output current 1<sub>γ</sub> from an input voltage V<sub>χ</sub>.

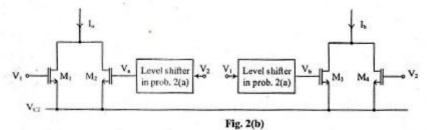

### Problem (2) [15 pts]:

- (a) For the level shifter circuit shown in Fig. 2(a), assuming M<sub>a</sub> and M<sub>b</sub> are matched and operating in the saturation region, show that: V<sub>b</sub> = V<sub>i</sub> V<sub>C1</sub> + V<sub>C2</sub>.

- (b) The level shifter in prob. 2(a) is used in the circuit shown in Fig. 2(b) to implement MOS multiplier. Show that:

$I_{ext} = I_{a} - I_{b} = K(V_{C1} - V_{C2})(V_{1} - V_{2})$ , where K is the

transconductance parameter of the transistors M1, M2, M3, and M4.

Fig. 2(a)

Page 1 of 3

Electronics 3 (ECE301) Final Term Exam 09/01/2016

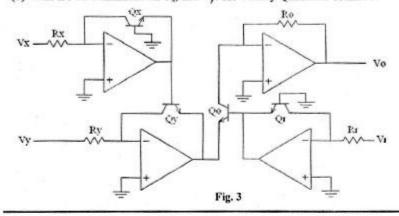

# Problem (3) [10 pts]:

A log-antilog analog multiplier is shown in Fig. 3. The output voltage  $V_o$  is a function of the product of two inputs  $V_x$  and  $V_y$ .

- (a) Find the relation between the output  $V_o$  and the input voltages  $V_x$ ,  $V_y$ , and  $V_r$ .

- (b) What are the limitations on Vs, and Vy? How many Quadrants obtained?

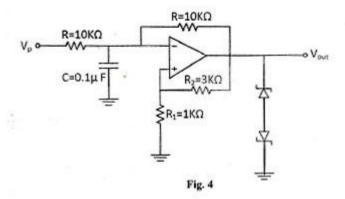

<u>Problem (4) [15 pts]</u>: An Asymmetrical SQW generator is shown below, where  $V_P$  is a constant D.C. voltage of 2V. The zener diodes are assumed ideal with  $V_Z$ =6V and  $V_{Don}$ =0V.

- (a) Sketch the output voltage waveform and the capacitor voltage waveform.

- (b) Find the frequency of the free running circuit.

Page 2 of 3

# Electronics 3 (ECE301) Final Term Exam 09/01/2016

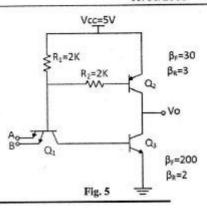

**Problem (5) [15 pts]:** For the TTL logic gate shown in Fig. 5,  $\beta_F = 200$  and  $\beta_R = 2$  for the NPN transistors  $Q_1$  and  $Q_3$ , while  $\beta_F = 30$  and  $\beta_R = 3$  for the PNP transistor  $Q_2$ :

- (a) Calculate Von and Vol.

- (b) What is the average static power consumption? (assuming 50% duty cycle)

- (c) What are the input currents in the two logic states?

- (d) What is the fan out capability of the gate?

- (e) What is the logic function of the gate?

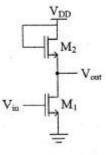

<u>Problem (6) [15 pts]:</u> Consider the enhancement-load inverter shown in Fig. 6.  $V_{T0}$ =1V,  $(W/L)_1$ =4,  $(W/L)_2$ =1/4,  $\mu_D C_{ox}$ =20 $\mu$ A/ $V^2$  and  $V_{DD}$ =5V.

- (a) Sketch the VTC of the inverter showing the mode of operation for M<sub>1</sub> in each region.

- (b) Find VoH, VoL, VIH, VIL and hence find NMH and NML.

- (c) Find the static power dissipation

- (d) Find the current available for discharging a load capacitor when V<sub>I</sub>=V<sub>OH</sub> and V<sub>O</sub>=4V and IV.

- (e) Realize the following function: F=(A+B)(C+D)

Fig. 6

# Problem (7) [10 pts]:

Design a 3-bit folded resistor-string D/A converter. Use 2 to 1-of-4 decoder with the most significant two bits (b<sub>1</sub>b<sub>2</sub>) to decode word lines, and use 1 to 1-of-2 decoder with the least significant bit (b<sub>3</sub>) to decode bit lines. Clearly show your transistor connections.

### Best Wishes!

Dr. Mohammed A. Hassan